< Digitale Schaltungstechnik

In diesem Kapitel geht es darum, die Vorteile der Beidflanken-Triggerung aufzuzeigen.

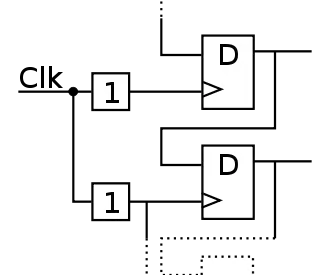

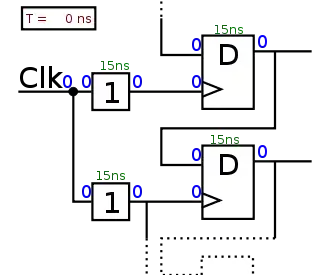

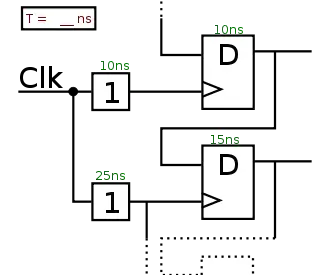

| Wir gehen von dieser Schaltung aus: |  |

| Es handelt sich nur um einen groben Auszug aus einer möglichen Schaltung; in der Praxis wird sich kaum eine derartige Schaltung finden. | |

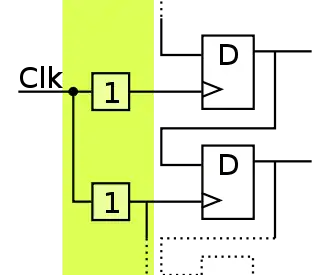

| Dieser Teil stellt eine Taktverteilung dar. |  |

| So etwas kann nötig sein, wenn der Taktgeber alleine z.B. maximal 10 Gatter ansteuern kann, wir aber sagen wir fünfzig haben. Durch so eine Schaltung muss der Taktgeber nur 5 Buffer treiben, die jeweils 10 Gatter ansteuern. | |

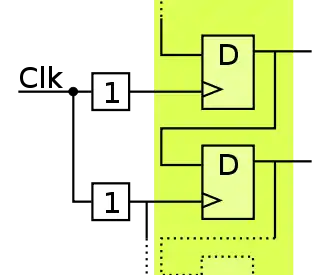

| Hier haben wir zwei Datenregister, die als Schieberegister geschaltet sind |  |

| Im kompletten Schema wären oben und unten noch weitere Flipflops. Zur Vereinfachung haben wir sie weggelassen. |

Idealfall

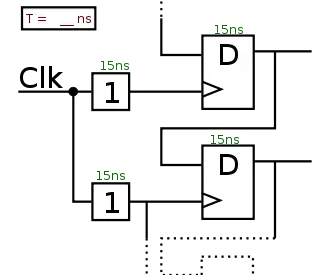

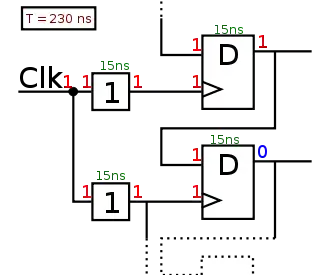

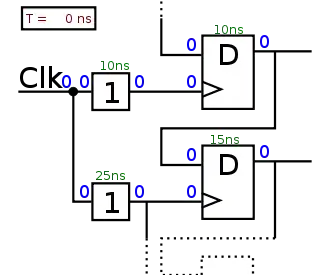

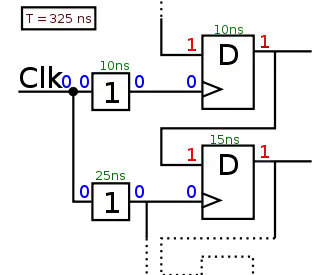

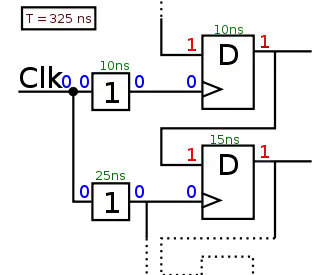

| Die Schaltung von oben ist nun ergänzt mit den Signallaufzeiten: |  |

| Die Startbedienung nehmen wir wie bisher einfach mit 0 an: |  |

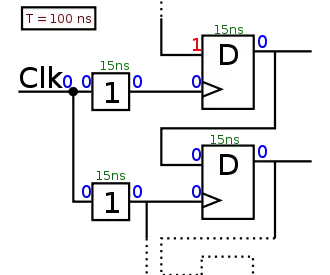

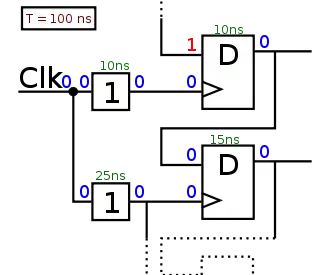

| Nach 100ns liegt am oberen Flipflop eine 1 an: |  |

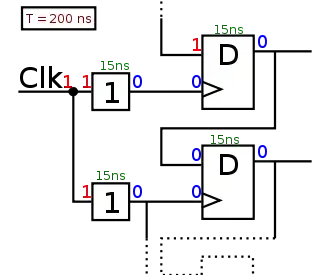

| Nach weiteren 100ns legen wir Clock auf 1: |  |

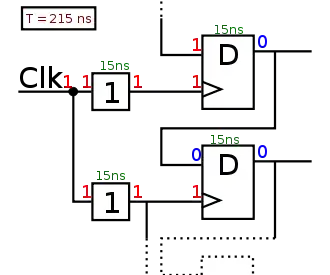

| Nach weiteren 15ns (der Gatterlaufzeit der Clocktreiber) gehen die Clocktreiber auf 1: |  |

| Nach weiteren 15ns (der Gatterlaufzeit des D-Flipflops) reagieren die Flipflops |  |

| |

|

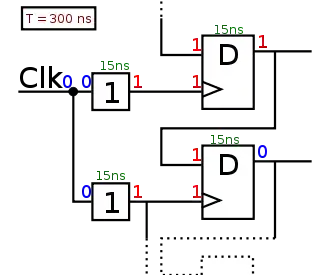

Unguter Fall

Die Laufzeitverzögerung zweier Gatter muss nicht unbedingt gleich sein. Gründe dafür können Herstelltoleranzen sein, unterschiedlich lange Leitungen usw.

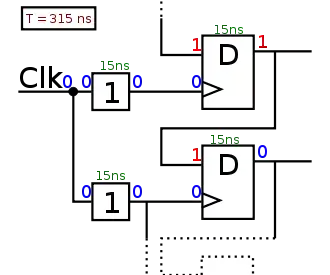

| Wir nehmen an, dass der obere Schaltungsteil eine kürzere Signallaufzeit hat, als der untere Schaltungsteil: |  |

| Das kann beispielsweise bei Ungünstiger Leitungsführung auf der Leiterplatte vorkommen. | |

| Wir nehmen an, dass am Anfang alle Bauteile auf Low sind: |  |

| Dann lagen wir ein High am ersten Flipflop an: |  |

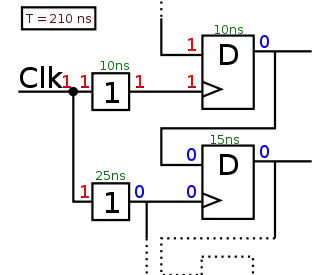

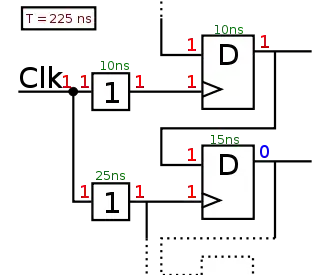

| Nach 200ns aktivieren wir das Clock Signal. Nach 10ns kommt das Clocksignal durch den ersten Treiber zum ersten Flipflop: |  |

| Nach weiteren 10ns reagiert das Flipflop: |  |

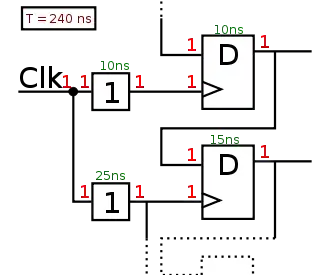

| Nach weiteren 5ns (also 25ns nach dem wir das Clock Signal angelegt haben), reagiert der zweite Treiber: |  |

| Zubeachten ist: Das Signal vom ersten Flipflop hat nun sozusagen den Clock vom zweiten Flipflop überhollt. | |

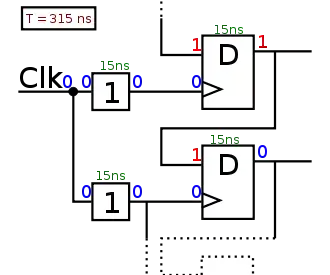

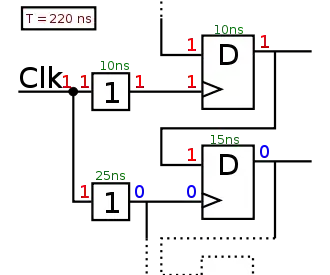

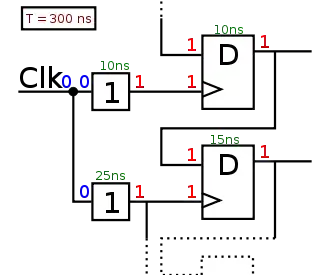

| Das zweite Flipflop braucht nach anliegen des CLocksignals noch 15ns bis es reagiert: |  |

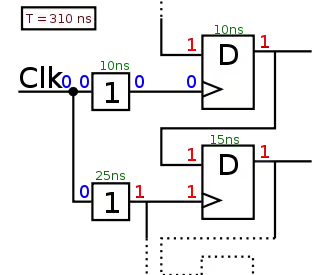

| Nun, setzen wir das CLock signal wieder auf Low: |  |

| Wieder geben die Treiber die Signale erst verzögert weiter: |  |

|

Vergleich

|

|

Lösung

Das Problem lässt sich unter anderem mit Master-Slave-Flip-Flops lösen: Digitale Schaltungstechnik/ Flipflop/ JK-Flipflop MS/ Herleitung

This article is issued from Wikibooks. The text is licensed under Creative Commons - Attribution - Sharealike. Additional terms may apply for the media files.